Basic core counter state. More...

#include <cpucounters.h>

Public Member Functions | |

| BasicCounterState & | operator+= (const BasicCounterState &o) |

| int32 | getThermalHeadroom () const |

| Returns current thermal headroom below TjMax. | |

Protected Member Functions | |

| void | readAndAggregate (SafeMsrHandle *) |

Friends | |

| class | PCM |

| template<class CounterStateType > | |

| double | getExecUsage (const CounterStateType &before, const CounterStateType &after) |

| Computes average number of retired instructions per time intervall. More... | |

| template<class CounterStateType > | |

| double | getIPC (const CounterStateType &before, const CounterStateType &after) |

| Computes average number of retired instructions per core cycle (IPC) More... | |

| template<class CounterStateType > | |

| double | getAverageFrequency (const CounterStateType &before, const CounterStateType &after) |

| Computes average core frequency also taking Intel Turbo Boost technology into account. More... | |

| template<class CounterStateType > | |

| double | getActiveAverageFrequency (const CounterStateType &before, const CounterStateType &after) |

| Computes average core frequency when not in powersaving C0-state (also taking Intel Turbo Boost technology into account) More... | |

| template<class CounterStateType > | |

| double | getCyclesLostDueL3CacheMisses (const CounterStateType &before, const CounterStateType &after) |

| Estimates how many core cycles were potentially lost due to L3 cache misses. More... | |

| template<class CounterStateType > | |

| double | getCyclesLostDueL2CacheMisses (const CounterStateType &before, const CounterStateType &after) |

| Estimates how many core cycles were potentially lost due to missing L2 cache but still hitting L3 cache. More... | |

| template<class CounterStateType > | |

| double | getRelativeFrequency (const CounterStateType &before, const CounterStateType &after) |

| Computes average core frequency also taking Intel Turbo Boost technology into account. More... | |

| template<class CounterStateType > | |

| double | getActiveRelativeFrequency (const CounterStateType &before, const CounterStateType &after) |

| Computes average core frequency when not in powersaving C0-state (also taking Intel Turbo Boost technology into account) More... | |

| template<class CounterStateType > | |

| double | getL2CacheHitRatio (const CounterStateType &before, const CounterStateType &after) |

| Computes L2 cache hit ratio. More... | |

| template<class CounterStateType > | |

| double | getL3CacheHitRatio (const CounterStateType &before, const CounterStateType &after) |

| Computes L3 cache hit ratio. More... | |

| template<class CounterStateType > | |

| uint64 | getL3CacheMisses (const CounterStateType &before, const CounterStateType &after) |

| Computes number of L3 cache misses. More... | |

| template<class CounterStateType > | |

| uint64 | getL2CacheMisses (const CounterStateType &before, const CounterStateType &after) |

| Computes number of L2 cache misses. More... | |

| template<class CounterStateType > | |

| uint64 | getL2CacheHits (const CounterStateType &before, const CounterStateType &after) |

| Computes number of L2 cache hits. More... | |

| template<class CounterStateType > | |

| uint64 | getL3CacheOccupancy (const CounterStateType &now) |

| Computes L3 Cache Occupancy. More... | |

| template<class CounterStateType > | |

| uint64 | getCycles (const CounterStateType &before, const CounterStateType &after) |

| Computes the number core clock cycles when signal on a specific core is running (not halted) More... | |

| template<class CounterStateType > | |

| uint64 | getInstructionsRetired (const CounterStateType &before, const CounterStateType &after) |

| Computes the number of retired instructions. More... | |

| template<class CounterStateType > | |

| uint64 | getCycles (const CounterStateType &now) |

| Computes the number executed core clock cycles. More... | |

| template<class CounterStateType > | |

| uint64 | getInstructionsRetired (const CounterStateType &now) |

| Computes the number of retired instructions. More... | |

| template<class CounterStateType > | |

| uint64 | getL3CacheHitsNoSnoop (const CounterStateType &before, const CounterStateType &after) |

| Computes number of L3 cache hits where no snooping in sibling L2 caches had to be done. More... | |

| template<class CounterStateType > | |

| uint64 | getL3CacheHitsSnoop (const CounterStateType &before, const CounterStateType &after) |

| Computes number of L3 cache hits where snooping in sibling L2 caches had to be done. More... | |

| template<class CounterStateType > | |

| uint64 | getL3CacheHits (const CounterStateType &before, const CounterStateType &after) |

| Computes total number of L3 cache hits. More... | |

| template<class CounterStateType > | |

| uint64 | getNumberOfCustomEvents (int32 eventCounterNr, const CounterStateType &before, const CounterStateType &after) |

| Returns the number of occured custom core events. More... | |

| template<class CounterStateType > | |

| uint64 | getInvariantTSC (const CounterStateType &before, const CounterStateType &after) |

| Computes number of invariant time stamp counter ticks. More... | |

| template<class CounterStateType > | |

| uint64 | getRefCycles (const CounterStateType &before, const CounterStateType &after) |

| Computes the number of reference clock cycles while clock signal on the core is running. More... | |

| template<class CounterStateType > | |

| double | getCoreCStateResidency (int state, const CounterStateType &before, const CounterStateType &after) |

| Computes residency in the core C-state. More... | |

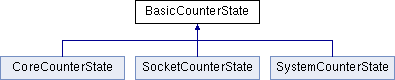

Detailed Description

Basic core counter state.

Intended only for derivation, but not for the direct use

Friends And Related Function Documentation

|

friend |

Computes average core frequency when not in powersaving C0-state (also taking Intel Turbo Boost technology into account)

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- frequency in Hz

|

friend |

Computes average core frequency when not in powersaving C0-state (also taking Intel Turbo Boost technology into account)

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- Fraction of nominal frequency (if >1.0 then Turbo was working during the measurement)

|

friend |

Computes average core frequency also taking Intel Turbo Boost technology into account.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- frequency in Hz

|

friend |

Computes residency in the core C-state.

- Parameters

-

state C-state before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- residence ratio (0..1): 0 - 0%, 1.0 - 100%

|

friend |

Computes the number core clock cycles when signal on a specific core is running (not halted)

Returns number of used cycles (halted cyles are not counted). The counter does not advance in the following conditions:

- an ACPI C-state is other than C0 for normal operation

- HLT

- STPCLK+ pin is asserted

- being throttled by TM1

- during the frequency switching phase of a performance state transition

The performance counter for this event counts across performance state transitions using different core clock frequencies

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- number core clock cycles

|

friend |

Computes the number executed core clock cycles.

Returns number of used cycles (halted cyles are not counted).

- Parameters

-

now Current CPU counter state

- Returns

- number core clock cycles

|

friend |

Estimates how many core cycles were potentially lost due to missing L2 cache but still hitting L3 cache.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Currently not supported on Intel(R) Atom(tm) processor

- Returns

- ratio that is usually beetween 0 and 1 ; in some cases could be >1.0 due to a lower access latency estimation

|

friend |

Estimates how many core cycles were potentially lost due to L3 cache misses.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- ratio that is usually beetween 0 and 1 ; in some cases could be >1.0 due to a lower memory latency estimation

|

friend |

Computes average number of retired instructions per time intervall.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- usage

|

friend |

Computes the number of retired instructions.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- number of retired instructions

|

friend |

Computes the number of retired instructions.

- Parameters

-

now Current CPU counter state

- Returns

- number of retired instructions

|

friend |

Computes number of invariant time stamp counter ticks.

This counter counts irrespectively of C-, P- or T-states

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- number of time stamp counter ticks

|

friend |

Computes average number of retired instructions per core cycle (IPC)

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- IPC

|

friend |

Computes L2 cache hit ratio.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- value between 0 and 1

|

friend |

Computes number of L2 cache hits.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of hits

|

friend |

Computes number of L2 cache misses.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of misses

|

friend |

Computes L3 cache hit ratio.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- value between 0 and 1

|

friend |

Computes total number of L3 cache hits.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of hits

|

friend |

Computes number of L3 cache hits where no snooping in sibling L2 caches had to be done.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of hits

|

friend |

Computes number of L3 cache hits where snooping in sibling L2 caches had to be done.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of hits

|

friend |

Computes number of L3 cache misses.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Warning

- Works only in the DEFAULT_EVENTS programming mode (see program() method)

- Returns

- number of misses

|

friend |

Computes L3 Cache Occupancy.

|

friend |

Returns the number of occured custom core events.

Read number of events programmed with the CUSTOM_CORE_EVENTS

- Parameters

-

eventCounterNr Event/counter number (value from 0 to 3) before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- Number of bytes

|

friend |

Computes the number of reference clock cycles while clock signal on the core is running.

The reference clock operates at a fixed frequency, irrespective of core frequency changes due to performance state transitions. See Intel(r) Software Developer's Manual for more details

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- number core clock cycles

|

friend |

Computes average core frequency also taking Intel Turbo Boost technology into account.

- Parameters

-

before CPU counter state before the experiment after CPU counter state after the experiment

- Returns

- Fraction of nominal frequency

The documentation for this class was generated from the following files:

1.8.7

1.8.7